Пока продолжение рассказа о коммуникационных фабриках по не зависящим от меня причинам откладывается, хотелось бы осветить другую тему.

С 8 по 12 октября в Подмосковье проходила крупнейшая в России конференция, посвященная проблемам разработки микро- и наноэлектронных систем. И хоть сама конференция оставила скорее негативное впечатление, но одно из выступлений выделялось из общей массы и, вероятно, будет интересно уважаемым читателям. Речь об аналитическом докладе «Life with «dark» silicon. Power and termal problems in future platforms», который представлял Mike Kishinevsky (Principal Engineer, Strategic CAD Labs, Intel Corp.). Я постараюсь рассказать об основных идеях этого доклада, используя материалы конференции и сторонние источники.

Что такое «темный» кремний

Итак, как всем известно, в далеком 1965 году, Гордон Мур, один из основателей корпорации Intel сформулировал наблюдение, в дальнейшем получившее название «закон Мура». [1] Согласно этому наблюдение количество транзисторов, размещаемых на кремниевом кристалле, удваивается приблизительно каждые два года. Данная тенденция сохраняется на протяжении более чем 45 лет, благодаря появлению всё более и более сложных технологических процессов. Сейчас активно используется 22nm техпроцесс, 14nm появится в ближайшие 1-2 года, и 10nm также не за горами. [2]

Если подобная тенденция сохранится, то к 2022 году количество транзисторов внутри одной микросхемы достигнет триллиона, а число слоев металлизации (используются для формирования связей между транзисторами) достигнет 14-18 штук – это необходимо для того, чтобы эффективно объединить столь огромное число транзисторов в единую систему. [3] Но, к сожалению, не всё столь безоблачно.

Согласно зависимости, известной как закон Деннарда, при масштабировании техпроцесса в S раз, вычислительная мощность (в идеальных условиях) возрастает как S^3. Кроме того, такой рост происходит без дополнительных накладных расходов энергопотребления. Это объясняется тем, что на той же площади помещается в S^2 больше транзисторов выполняющих полезную работу, и такие транзисторы могут работать на большей в S раз тактовой частоте. При этом емкость и рабочее напряжение могут быть уменьшены в S раз. [4]

На практике, по мере уменьшения технологического процесса, растут токи утечки, протекающие через закрытый транзистор, что является основным фактором роста энергопотребления, которое в идеальном случае бы не менялось. В результате такого роста, в двухтысячных тепловыделение некоторых процессоров приближалось к тому, что можно наблюдать в недрах ядерного реактора, а энергопотребление ассоциировалось скорее со сварочным аппаратом, а не с высокотехнологичным устройством. [5]

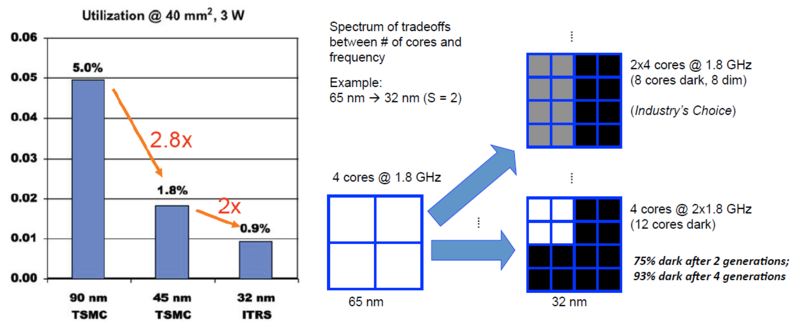

Необходимость оставаться в определенных рамках энергопотребления привела к появлению ограничения называемого Utilization Wall, согласно которому с каждым новым техпроцессом и в отсутствие радикальных технологических изменений, доля площади кристалла задействованной в активной работе (буквально, где могут переключаться транзисторы) убывает экспоненциально. Причем эта площадь измеряется единицами или даже долями процентов. [6] Оставшаяся бОльшая часть кристалла, не задействованная в данный момент в работе, и получила название «тёмный» кремний («Dark» Silicon).

Utilization Wall

В результате разработчики новых микропроцессоров должны быть уверены, что в любой момент работы бОльшая часть кристалла является «темным» или «тусклым» кремнием – бездействует или работает на значительно пониженной тактовой частоте.

Майкл Тейлор в своей статье «Is Dark Silicon Useful? Harnessing the Four Horsemen of the Coming Dark Silicon Apocalypse»[7] упоминает о четырех «всадниках Апокалипсиса» — четырех основных подходах, позволяющих микроэлектронике процветать в эпоху «тёмного» кремния. Эти подходы: использование новых достижений технологического процесса, параллелизация для энергоэффективности, специализация и управление энергопотреблением. Кроме того, важную роль играет оптимизация на системном уровне. О данных подходах и пойдет речь дальше.

«The Deus Ex Machina Horseman» или прогресс технологического процесса.

Из всех четырех всадников кремниевого апокалиспсиса, это, безусловно, самый непредсказуемый. В литературе или театре Deus Ex Machina относится к сюжету, в котором главные герои, кажется, совершенно обречены, но затем что-то совершенно неожиданное и непредсказуемое приходит из ниоткуда, чтобы спасти ситуацию.

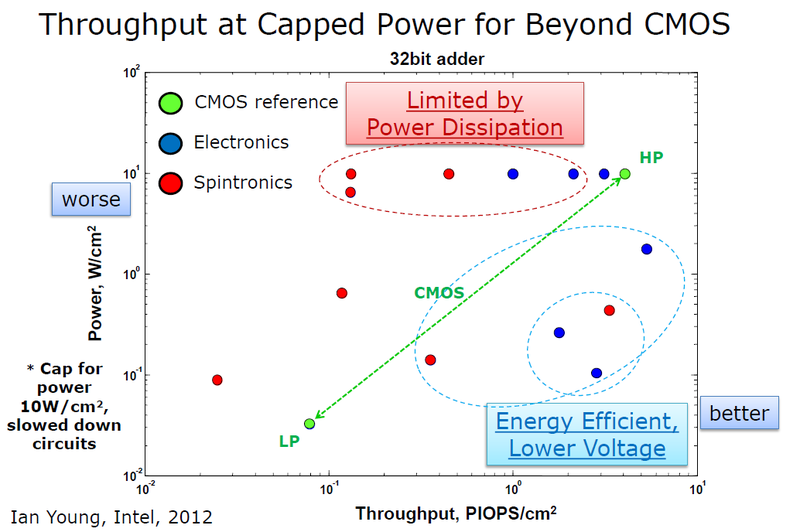

В случае тёмного кремния, Deus Ex Machina мог бы стать научный прорыв в полупроводниковой технологии. Однако, подобные прорывы должны быть достаточно фундаментальными. И, скорее всего, в недалеком будущем подобный прорыв потребует использования транзисторов отличных от традиционной MOSFET технологии. Причиной является то, что токи утечки определяются фундаментальными физическими принципами. Хотя такие инновации как изобретение FinFET / Tri-Gate транзисторов или использование High-K диэлектриков и т.д., представляют значительные достижения. Но являются скорее одноразовыми улучшениями, а не масштабируемыми изменениями. [8] Не буду останавливаться на преимуществах Tri-Gate, т.к. о них писалось уже не раз 🙂

Разработки технологий, способных прийти на смену MOSFET ведутся уже давно. Два потенциальных и (на данный момент) наиболее перспективных кандидата: это TFET-транзисторы и нано-электро-механические переключатели. Есть причины считать, что обе эти технологии могут обеспечить уменьшение токов утечки на порядки, по сравнению с используемыми сейчас решениями, но, при этом, они всё еще очень далеки от промышленного использования.

Одним источником оптимизма о существовании прорывных технологий является производительность, энергоэффективность и плотность человеческого мозга. Мозг объединяет 100 триллионов синапсов, которые работают, потребляя менее 20W, и служат живым доказательством возможности высоко параллельных и при этом в основном «темных» вычислений.

Как итог, технологические достижения всё еще продолжают удивлять, уже сейчас существует ряд интересных альтернатив традиционной MOSFET-электронике. Но предсказать когда эти альтернативы доберутся до промышленного использования, а тем более, появление новых не представляется возможным.

«The Shrinking Horseman» и параллелизация для энергоэффективности

Из-за роста токов утечки по мере шкалирования техпроцесса, многоядерность микропроцессоров не может далее масштабироваться так же, как уменьшается занимаемая одним ядром площадь кристалла. При этом «темный» или «тусклый» кремний – экспоненциально более дешевый ресурс с точки зрения энергопотребления. Это заставляет обратиться к архитектурным решениям, позволяющим «расходовать» площадь кристалла, чтобы «приобрести» энергоэффективность. Приведенный на рисунке пример, показывает, как замена одного компаратора на два, работающих параллельно, но на вдвое меньшей частоте, позволяет сократить энергопотребление в 2.5 раза! [9] На практике, далеко не все узлы можно распараллелить на близкий к идеальному манер, но выигрыш с точки зрения энергопотребления будет всё равно ощутим.

Trade-off площади и энергопотребления

Немедленной реакцией на такой подход со стороны многих разработчиков было то, что «площадь кристалла – дорогой ресурс, почему бы просто не делать микропроцессоры меньше, вместо использования «тёмного» кремния?» Однако, это самый пессимистичный сценарий. И хотя все чипы могут в конечном итоге претерпеть сокращение площади, такой взгляд упускает ряд второстепенных факторов, играющих решающую роль.

Во-первых, стоит сказать, что «темный» кремний не значит, «пустой», «бесполезный» или «неиспользуемый» кремний. Даже в лучшие дни CMOS технологии, микропроцессор и другие схемы были полны темной логики, которая используется только для некоторых задач. Например, блок выполнения SSE инструкций на x86 не используются для нерегулярных вычислений, а удвоение LLC (последнего уровня кэша) даёт выигрыш только для небольшого круга задач.

Также заслуживает внимания финансовая сторона сокращения площади кристалла. В том, что производить меньшие кристаллы выгоднее, есть некоторая правда. В конце-концов, разработчики микропроцессоров тратят массу усилий, пытаясь попасть в доступный бюджет по занимаемой площади. Меньшие по площади процессорные кристаллы линейно (или еще более) дешевле. Кроме того, для них выше показатели выхода годных при производстве. Но экспоненциально меньшие по площади процессоры не будут экспоненциально дешевле из-за затрат на разработку, изготовление литографических масок, корпусирование и т. д. А эти затраты тоже должны как-то амортизироваться, что приведет к росту стоимости за единицу площади кремния. Что, в свою очередь, сделает переход на новый техпроцесс финансово менее привлекательным и приведет к несчастливому экономическому концу закона Мура. Также существует ряд других причин, основанных на законах конкурентной экономики, объясняющих, почему сокращение площади — это крайне маловероятный сценарий, но не буду вдаваться в подробности, не слишком интересные техническому кругу читателей.

Ну и нельзя не упомянуть проблемы, связанные с корпусированием и рассеиванием тепла, возникающие при сокращении площади кристалла. Важным следствием экспоненциального сокращения площади является экспоненциальный рост удельной потребляемой мощности. Последние исследования в области анализа тепловых характеристик чипов многоядерных процессоров [10] показали, что пиковая температура горячей точки (hotspot) может быть смоделирована как Tmax = TDP * (Rconv + k/А). Где TDP — величина, показывающая, на отвод какой тепловой мощности рассчитана система охлаждения процессора, Rconv – характеристика радиатора (меньше – лучше), k – собирательная характеристика свойств микропроцессора, а A – занимаемая площадь. При экспоненциальном уменьшении площади, второе слагаемое становится доминирующим и приводит к экспоненциальному росту температуры. Необходимость же уберечь процессор от перегрева потребует пожертвовать частью его производительности.

Кроме того, сокращение площади также представляет целый ряд практических инженерных вопросов. Например, вертикальное соединение кремниевых пластин, с использованием технологий подобных Die Stacking требует наличия контактных площадок и прорезей в кремнии (TSVs), размер которых не может уменьшаться столь же легко. Кроме того, области подключения I/O также не масштабируются со скоростью закона Мура.

3-D интеграция и TSV в картинках 🙂

Как итог: дальше уменьшаться площадь микропроцессоров, скорее всего не будет (а если и будет, то очень медленно). Но если раньше дополнительные транзисторы, приносимые каждым новым поколением техпроцесса, использовались для повышения производительности (примерно в 1.4 раза за каждое поколение), то сейчас — для сокращения энергопотребления (примерно на 40% за каждое поколение)

Продолжение следует.

References

- Gordon Moore (1965). «Cramming more components onto integrated circuits»

- Mark Bohr, Intel, 2011

- Shekhar Borkar, Intel, 2010

- Mark Bohr, (2007) “A 30 Year Retrospective on Dennard’s MOSFET Scaling Paper”

- Fred Pollack, (1999) “New Microarchitecture Challenges in the Coming Generations of CMOS Process Technologies”, keynote at Micro

- Ganesh Venkatesh et al, (2010) “Conservation Cores: Reducing the Energy of Mature Computations”, ASPLOS 2010

- Michael Taylor, (2012) «Is Dark Silicon Useful? Harnessing the Four Horsemen of the Coming Dark Silicon Apocalypse», DAC 2012

- Ian Young, Intel, 2012

- Anantha Chandrakasan et al, (1992) “Low-Power CMOS Digital Design”

- W. Huang et al, (2008) «Many-core design from a thermal perspective." DAC 2008.

ссылка на оригинал статьи http://habrahabr.ru/company/intel/blog/158223/

Добавить комментарий