Многие начинающие разработчики часто недооценивают влияние асинхронности на работу цифровых схем. В проектах с одним тактовым генератором сложностей не возникает: схема полностью синхронна, и от разработчика требуется только соблюдать требования Setup и Hold. Но как только в системе появляется второй тактовый генератор, возникает проблема CDC – Clock Domains Crossing, связанная с асинхронностью работы участков схемы, работающих от независимых (асинхронных) генераторов. На практике эта проблема выливается в усложнение маршрута проектирования, связанное с особенностями статического временного анализа в САПР, а в железе проявляется в виде такого эффекта как метастабильность, и аномальное поведение триггеров. Собственно, о метастабильности здесь (https://habrahabr.ru/post/254869/) уже писали, но я предлагаю чуть глубже разобраться в проблеме.

В начале несколько вводных слов. О таких критичных для работы параметрах триггера как setup и hold подробно написано здесь https://habrahabr.ru/post/302806/. В двух словах, вблизи момента прихода тактового сигнала на вход триггера существует некий минимальный интервал времени, внутри которого сигнал на информационном входе должен оставаться стабильным. Если изменение сигнала происходит за пределами этого интервала, триггер срабатывает правильно. Это минимальные требования, которые должен соблюдать разработчик, проектируя схему с одним тактовым генератором. И даже если в проекте используется несколько кратных частот, полученных из одной опорной, схема также считается синхронной, а максимум, о чем следует заботиться при проектировании, это соблюдение Setup и Hold.

Теперь представим, что в проекте используются два независимых источника тактирования. Все триггеры в схеме разделяются на два домена, по принципу управления от одной или другой опорной частоты. Между этими асинхронными друг другу доменами проходит граница в виде сигналов, сформированных на одной опорной частоте, и заходящих на информационные входы триггеров, работающих на другой частоте. Фактически, сигнал на входах триггеров оказывается асинхронен их тактовому импульсу, что означает, что требуемые времена Setup и Hold не могут быть выдержаны. В результате, в работе триггеров на границе двух доменов изредка возникают аномалии (фактически — сбои), которые на временном моделировании обычно обозначается как неопределенное состояние триггера X, и раскрашиваются на вейвформе красным цветом. В реальной схеме это аномальное состояние триггера может оказаться просто затянувшимся срабатыванием, поскольку для попадания триггера в область метастабильности, входной сигнал должен измениться в гораздо более узком отрезке времени, чем ts + th:

На рисунке показаны: tc – абсолютное время прихода фронта тактового импульса, являющееся нулевым отсчетом для оси Hold (направлена от ноля вправо), и оси Setup. Ось Setup направлена влево, поскольку время установки отсчитывается в отрицательном направлении от момента прихода фронта клока. Далее, ts и th – параметры Setup и Hold триггера: между отметками ts и th сигнал на информационном входе триггера обязан быть стабильным (красная область рисунка). Вне окна ts + th сигнал может меняться произвольно (синяя область рисунка). При изменении сигнала внутри окна ts + th, переключение триггера может сильно затянуться. Последний элемент рисунка – область метастабильности, выделена оранжевым цветом. Это некий интервал времени, при попадании в который поведение выходов триггера становится непредсказуемым, о чем будет подробно рассказано ниже. На практике, время th часто бывает отрицательным (окно ts + th по той или иной причине оказывается сдвинуто влево относительно нулевой отметки), а ширина области метастабильности должна определяться индивидуально для каждой схемы триггера и параметров транзисторов – экспериментально, либо с помощью спайс-моделирования.

Рассмотрим устройство классической схемы D-триггера и составляющей его RS-защелки:

Представим, что на вход R (Reset) защелки приходит короткий импульс с активным нулем, а на входе S (Set) – пассивный сигнал (лог. 1). Если импульс совсем короткий, то защелка может не переключиться. А если увеличить длительность импульса? Проведем серию экспериментов, подавая на вход защелки импульсы разной длительности. Следующий рисунок позаимствован из статьи Л.Р. Марино General Theory of Metastable Operation:

На рисунке обозначены две оси – напряжение на X и Y выходах RS-защелки. Отметки V0 и V1 – напряжение лог. 1 и лог. 0 выходов триггера, а Vm – напряжение, равное ½ Uпитания. На рисунке так же показано, что начальное состояние (Initial state) находится в точке плоскости {X=V1, Y=V0} — выходы триггера {X, Y} приняли логические значения {1,0}. На вход защелки S (Set) подан высокий потенциал (пассивное значение), а на вход R (Reset) подается импульс с активным нулем разной длительности (6-самый короткий, 1-самый длинный – изображено внизу рисунка). В соответствии с номером импульса на входе R, на рисунке показаны 6 траекторий переключения потенциалов пары выходов {Y,X}: для импульсов 1-3 происходит полное переключение триггера, для импульсов 5-6 триггер не переключится, а траектория 4 приводит триггер в центр зоны метастабильности (точка {Vm,Vm}), находящийся посередине между порогами лог. 1 и лог. 0.

Итак, мы показали, что подав на одно плечо защелки импульс недостаточной длительности, его энергии может не хватить для полного переключения. При большой длительности импульса, защелка обязана переключится. И, наконец, можно подобрать входной импульс такой длительности, что выходы защелки окажутся посередине между двумя стабильными состояниями. При этом, чем ближе к области метастабильности подталкивает выходы защелки энергия импульса, тем дольше потом эти выходы восстанавливают стабильное состояние.

Теперь обратимся к современной схеме D-триггера из библиотеки для 65нм, использующейся при проектировании ASIC:

На схеме по информационному входу D стоит ключ GD, первая защелка изображена в виде двух инверторов во встречном включении I1 и G1, проходной ключ SW разделяет защелки, а вторая защелка строится так же на двух инверторах во встречном включении I2 и G2. Выход для повышения скорости берется с левого плеча второй защелки. Триггер работает следующим образом: при CK=0 входной ключ пропускает сигнал на первую защелку с отключенной обратной связью G1, ключ между защелками закрыт, а вторая защелка находится в хранении, поскольку активна обратная связь G2. При CK=1 первая защелка отсекается от входа D, у нее активизируется обратная связь G1, отпирается ключ между защелками, а у второй защелки выключается обратная связь – данные из первой защелки переписываются во вторую. Если сигнал D снимается раньше прихода переднего фронта CK, мы получаем на входе первой защелки импульс с активным нулем, чья длительность зависит только от соотношения фронтов CK и D. Таким образом, ситуация аналогична рассмотренной с RS-защелкой: энергия импульса на одном из плеч может переключить защелку, не переключить, либо — ввести защелку в состояние метастабильности. В статье Л.Р. Марино математически доказано, что выходы абсолютно любого триггера, независимо от его конструкции, могут принимать метастабильное состояние.

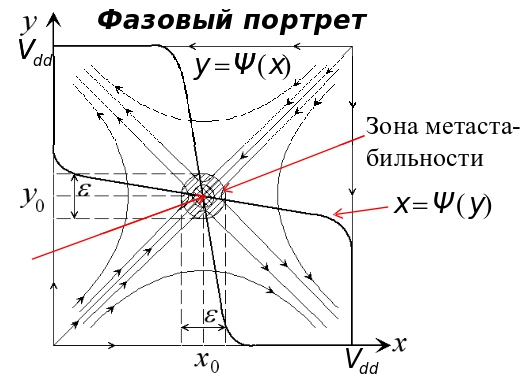

Попробуем рассмотреть все возможные состояния выходов защелки; для этого построим еще один график с двумя осями-потенциалами выходов. График позаимствован из лекций по логическому проектированию д.т.н., профессора В.Б. Мараховского:

График почти такой же, как и в статье Л.Р. Марино, но стрелками изображены траектории возможного поведения выходов защелки. Двигаясь по траекториям, выходы защелки в конечном счете переключатся в устойчивое логическое состояние {1,0} или {0,1}, соответствующее состоянию на входах (состояние входа защелкнется). Но при попадании потенциала выходов в некую область по центру графика, предсказать конечное состояние выходов невозможно. Это область неустойчивого равновесия (метастабильности), на выход из которой могут влиять только случайные факторы, такие как тепловой шум. Конечное состояние выходов защелки при завершении метастабильности заранее неизвестно – оно может быть любым ({1,0} или {0,1}). Размер области метастабильности измеряется экспериментально, либо вычисляется с помощью спайс-моделирования. Следует отметить, что на практике метастабильность проявляется не только в виде статичного потенциала, равного ½ Uпитания, но также и в виде слабых пульсаций вблизи этой точки. Другим важным свойством метастабильности является непредсказуемость времени установления защелки в стабильное состояние. Как известно, время выхода защелки из метастабильного состояния описывается распределением Пуассона, и в теории может быть бесконечно долгим. Таким образом, нельзя заранее предсказать не только конечное состояние триггера после выхода из метастабильности, но и продолжительность метастабильного состояния во времени. Впрочем, если сигнал на входе триггера не меняется и в следующем такте, то максимальная продолжительность метастабильного состояния выходов триггера на границе двух доменов не превышает длительности тактового импульса.

Формулы и методики расчета размеров области метастабильности и частоты сбоев можно посмотреть в статье Variability in Multistage Synchronizers. Приведу лишь результаты расчетов частоты сбоев из этой статьи. В качестве синхронизатора использовались схемы последовательного соединения 2х, 3х и 4х триггеров, работающих от импульса с периодом 800пс, и диапазоном частот входного сигнала от 600пс до 2нс.

На графике по вертикальной оси отложен MTBF в годах – срок между сбоями (попадание в метастабильное состояние — сбой) при использовании разных синхронизаторов на входе в домен, работающий от такта с периодом 800пс. По горизонтали отложен период тактового импульса домена – источника сигнала. Как видно из рисунка, чем больше триггеров в цепочке синхронизатора, тем реже происходят сбои.

Выводы:

1. Время переключения триггера целиком и полностью зависит от длительности управляющего импульса на входе первой защелки, который получается сдвигом фазы прихода сигнала к тактовому импульсу на входах триггера. При переключении сигнала за границами интервала ts + th, триггер переключается правильно, и за заранее известное время. Но, если входной сигнал поменялся внутри этого интервала, то стабильного состояния триггер достигает тем дольше, чем ближе к зоне метастабильности он оказался. Если же выходы триггера оказались внутри зоны метастабильности, их конечное логическое состояние и время срабатывания не могут быть предсказаны.

2. Метастабильность выходов триггера выглядит на осциллографе как уровень потенциала выходов, равный ½ Uпитания, либо как слабые пульсации вблизи этого уровня. При этом в инверторах схемы триггера течет сквозной ток между шинами земли и питания. Но поскольку сопротивление открытого канала в n- и p- транзисторах измеряется килоОмами, то сквозной ток не оказывает заметного влияния на такие явления как общее потребление схемы, просадка питания (IR drop), и электромиграция.

3. На частотах около гигагерца сбой (вследствие метастабильности) в триггере на границе двух доменов происходит раз в несколько секунд. Бороться с метастабильностью помогает использование в качестве синхронизатора двух и более последовательно включенных триггеров. При использовании двух триггеров, сбой на выходе синхронизатора случается уже раз в год; трех триггеров – раз в тысячу лет; четырех триггеров – раз в 10 миллиардов лет. Снижение рабочей частоты влияет на частоту сбоев экспоненциально: при использовании синхронизатора из двух триггеров и частоте около 500МГц, интервал сбоев увеличится на несколько порядков – до одного сбоя в миллион лет. Поэтому, если Вы проектируете схему с частотами под гигагерц, постарайтесь использовать как можно меньше асинхронных доменов, либо увеличивайте число последовательно включенных триггеров в синхронизаторах до трех.

4. На частоту сбоев сильно влияют паразитные емкости выходов первой и второй защелок (составляющих триггер), которые зависят от параметров используемых транзисторов и от схемы триггера. Другими словами, меняя параметры транзисторов и схему триггера, можно косвенно влиять и на периодичность возникновения метастабильности на выходах этого триггера. Рецепт годится, только если Вы проектируете собственную библиотеку элементов.

5. С точки зрения статического временного анализа, все пути между асинхронными доменами должны быть описаны sdc констрейнтами set_false_path.

Метастабильность триггеров в России никем не изучается (поправьте, если не прав), но на практике разработчику достаточно следовать тем простым рекомендациям, что даны выше; надеюсь, это кому-нибудь окажется полезным.

ссылка на оригинал статьи https://habrahabr.ru/post/317514/

Добавить комментарий