Здравствуйте! Меня зовут Станислав Полонский. Я представляю Samsung Advanced Institute of Technology (SAIT) — научно-исследовательский центр, специализирующийся на передовых технологиях будущего.

Сегодня мы поговорим о том, что такое архитектура RISC-V (читается, как «РИСК-Пять»). Я расскажу вам о прошлом и будущем этих процессоров, о том, почему эта архитектура так подходит для Интернета вещей, а в конце скажу, как можно продолжить своё образование в этом направлении.

Масштабирование транзисторов (transistor scaling)

Итак, за последние 50 лет в микроэлектронике мы наблюдаем явление, которое называют «масштабированием транзисторов»: размер транзисторов уменьшился в сотни раз, а их энергопотребление возросло меньше, чем на порядок (рисунок 1). Это также называют масштабированием Деннарда.

Роберт Деннард работал в компании IBM и в 1974 году показал, что уменьшение размеров полевых транзисторов приводит к тому, что они работают быстрее, в то время как общее суммарное энерговыделение является более-менее постоянной величиной.

Однако, эта тенденция, длившаяся десятки лет, закончилась. Размеры транзисторов приближаются к атомным размерам. Я не ожидаю, что в будущем что-то сильно изменится — предел масштабирования достигнут.

Тенденции роста производительности процессоров

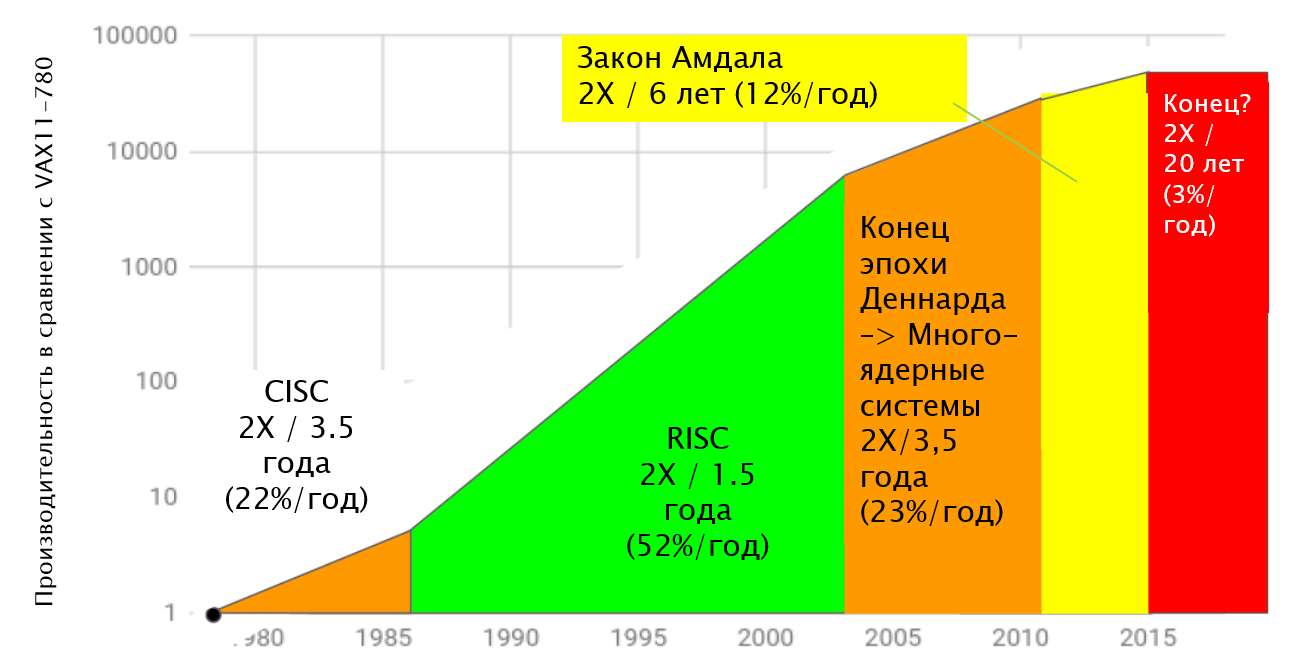

Если раньше мы говорили про одиночные транзисторы, то теперь мы говорим о системах, микропроцессорах, системах на чипе (system-on-chip). На рисунке 2 мы видим, как увеличилась их производительность.

Видно, что производительность увеличилась в сотни тысяч раз (масштаб на графике по вертикали логарифмический) начиная с 80-х годов до настоящего времени.

Вначале программисты имели дело с набором команд процессора, который назывался сложным (CISC — Complex Instruction Set Computer). Люди быстро разобрались с тем, чтобы упростить его и сделать RISC — Reduced Instruction Set Computer. И где-то с 80-х до середины нулевых годов это был основной драйвер роста производительности: транзисторы уменьшаются, архитектуры простые, производительность растет экспоненциально.

К концу эпохи Деннарда произошел переход к многоядерным системам, что добавило ещё производительности. Однако, тут было быстро достигнуто ограничение, обусловленное так называемым законом Амдала, когда производительность многоядерной системы ограничивается наиболее узким местом — доступом к общей памяти среди многочисленных ядер на микропроцессоре.

Сейчас мы находимся в красной зоне — конце масштабирования, насыщении производительности микропроцессоров. Закон Мура (рост производительности в два раза за два года) для микропроцессоров более-менее завершился.

Проблемы архитектуры x86

Что имеем сейчас? Хотя состоялся переход на RISC-процессоры, системы команд продолжали усложняться. Это связано с тем, что возникали новые приложения, а для этих новых приложений требовались новые команды. На рисунке 3 показан рост количества таких команд для архитектуры Intel x86.

Если в середине 70-х была едва ли сотня машинных команд, то сейчас их порядка трех тысяч. Это приводит к усложнению железа. При том, что RISC-железо не должно быть таким: слишком много команд и ограничений на дизайн микропроцессоров.

Сложность архитектуры x86 привела к низкой энергоэффективности, и, как следствие, более энергоэффективная архитектура ARM (Advanced RISC Machine) захватила рынок. Это показательный пример того, как важно поддерживать наборы компьютерных команд как можно более простыми.

Тенденции будущего

Что ждёт нас в будущем? По моему мнению, две важных тенденции:

-

Мы все знаем про революцию открытых исходников (Open Source) программного обеспечения (ПО). У нас есть компиляторы GCC (GNU Compiler Collection), операционные системы Linux, но есть проблемы, касающиеся открытых компьютерных архитектур (Instructions Set Architectures, ISA). Долгие годы это был удел мегакорпораций. Они контролировали компьютерные архитектуры.

-

Второй тренд касается специализированных архитектур (Domain Specific Architectures). Если раньше мы говорили про компьютеры фон Неймана, универсальные вычислители, то сейчас, в связи с тем, что рост производительности микропроцессоров более-менее закончился, его улучшение ожидается только за счёт специализации компьютерного железа. Примером тому могут быть графические процессоры, нейропроцессоры, тензорные (очень близки к нейропроцессорам) и data-процессоры (для обработки сетевых данных). Вы можете сказать, что специализированные архитектуры — это удел ASIC (Application-Specific Integrated Circuit). Это, действительно, так, но ASIC не программируемы. А хотелось бы совместить специализацию по областям с программируемостью.

Обращу также ваше внимание на специализированную архитектуру, которой уже, наверное, сто миллионов лет. Это человеческий мозг. Я не хочу сказать, что это доказывает, что специализированная архитектура – будущее микроэлектроники, просто иллюстрирую тот факт, что в голове у нас находится очень успешная специализированная архитектура.

Особенности RISC-V

Что такое RISC-V? Ещё в восьмидесятые годы ученые из университета Калифорнии в Беркли начали говорить о том, что упрощенные наборы команд превосходят сложные системы. RISC лучше, чем CISC. И это было доказано развитием микроэлектронной индустрии.

Почему RISC-V? Начиная с 80-ых годов и где-то до 2010 года эти парни из Беркли сделали несколько наборов архитектур и номер пять является их последней архитектурой. Она получила очень большую популярность, стала бурно развиваться, и теперь о ней знают очень многие люди.

Почему же такая популярность? Созрела потребность в открытой и свободной компьютерной архитектуре. Это хорошо работало в случае Linux, в случае движения открытых исходных текстов ПО. Это нравится академическим исследователям, это нравится маленьким компаниям. Далее интересна масштабируемость от микроконтроллеров до серверов — от «края» облака до самого облака, чтобы одна и та же архитектура покрывала самые различные приложения. Сейчас это не так. В серверах, в основном, используется архитектура Intel, в микроконтроллерах мы имеем ARM, MIPS (Microprocessor without Interlocked Pipeline Stages). Ещё одна важная вещь — компьютерная безопасность. Когда у вас открытые исходники, то их легче отладить. Если у вас открытые ядра, то никто не боится, что в них закладки.

Усложнения системы команд — накладные расходы с точки зрения компьютерного железа. В RISC-V отражен опыт десятилетий развития RISC-архитектур. При этом она простая, эффективная и мощная.

Международная организация RISC-V

Опыт работы с открытыми источниками ПО показал, насколько важно сообщество разработчиков. RISC-V имеет два смысла. Это набор компьютерных команд, а также международная организация RISC-V Foundation, которую недавно переименовали в RISC-V International. Она, собственно, контролирует эту архитектуру, но это не означает, что она препятствует её развитию. Каждый может стать членом этой организации, каждый может внести пассивный вклад в развитие архитектуры. И, что важно, организация старается позиционировать себя как политически нейтральная.

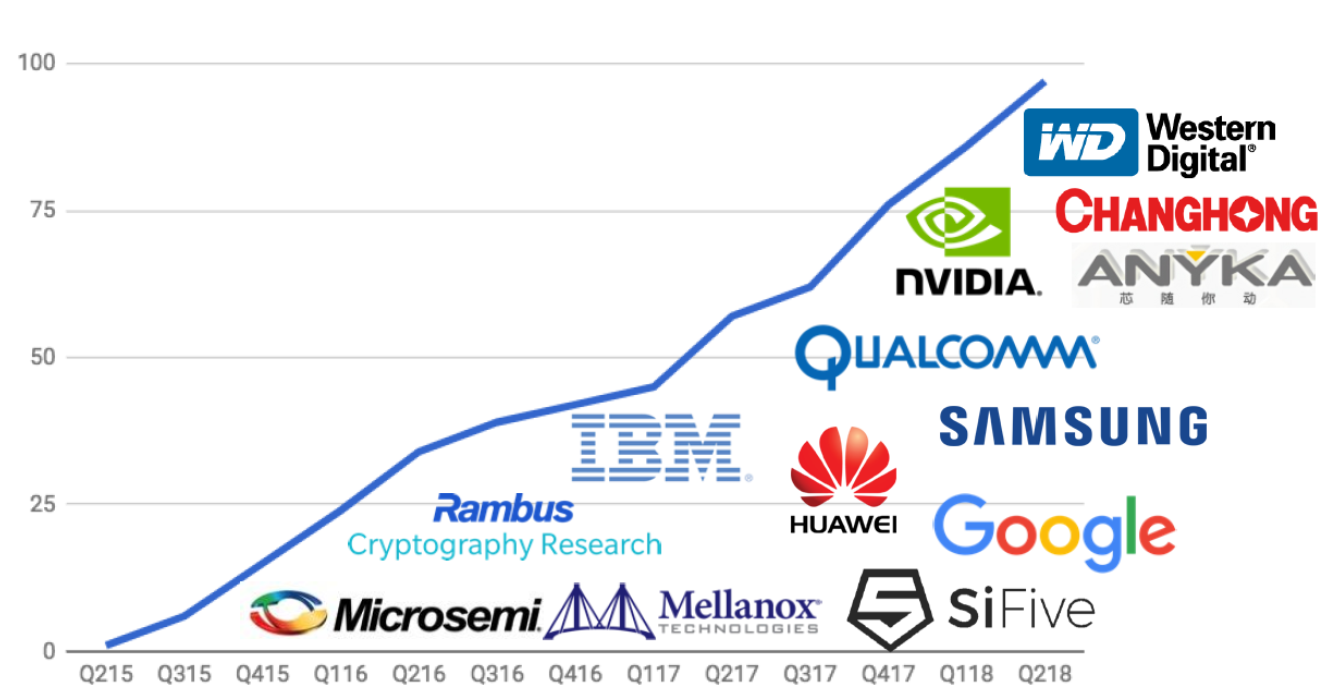

RISC-V International была создана в 2015 году. И сейчас она растёт очень быстро (смотрите рисунок 4).

Среди её членов, как маленькие компании, так и гиганты типа IBM, Samsung, Google. Профессор, который изобрёл эту архитектуру, создал компанию Silicon Five – очень известного, хотя и маленького игрока на этом фронте.

Об интересе со стороны крупных игроков говорят следующие факты:

-

Октябрь 2021 — Intel делает попытку приобрести SiFive;

-

Февраль 2022 — Intel объявляет о том, что инвестирует 1 млрд $ в развитие RISC-V;

-

Март 2022 — AMD размещает вакансии разработчиков RISC-V.

По состоянию на 2022 год она насчитывает 2,400+ участников и ~300 компаний. Такой рост позволяет нам говорить, что RISC-V – это серьёзно и надолго.

Характеристики архитектуры RISC-V

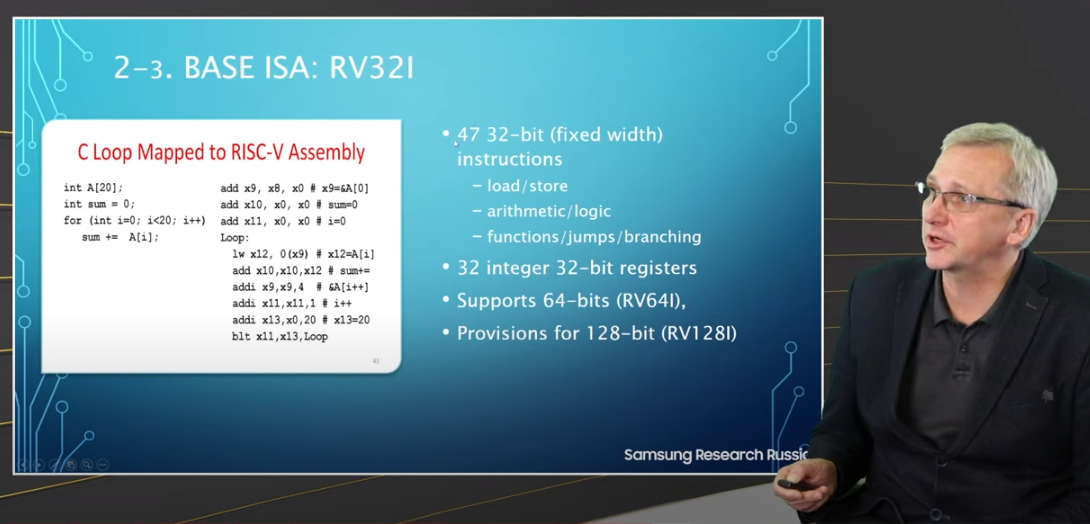

Не вдаваясь в технические подробности, остановлюсь на самых простых характеристиках архитектуры.

RV32I означает архитектуру RISC-V, 32-разрядную, I означает наличие целочисленной арифметики. Эти параметры — джентльменский набор для того, чтобы поднять операционную систему. Это базисная архитектура, которая позволяет запускать операционную систему на микропроцессоре.

Архитектура сама по себе очень простая. В ней всего 47 базисных команд. Эти команды фиксированной ширины по 32 бита. Это работа с памятью, арифметика, логика, работа с функциями. Архитектура поддерживает 32 32-битных регистра, архитектуру 64 бита (масштабирование очень важно), она будет называться RV64I. Также эта архитектура будет распространена на 128 бит (RV128I).

Простота важна, но также важна так называемая модульность. Если раньше компьютерные архитектуры были инкрементальными, то есть поверх старых команд добавлялись новые и в конце концов сложность архитектуры приводила к утере эффективности. В RISC-V мже не инкрементальная, а модульная системой команд.

Что это означает? Базисная система команд может быть расширена. Возьмите только то, что вам нужно. Например,

-

M — целочисленное умножение и деление (RV32IM, то есть процессор, поддерживающий базисную RV32I и целочисленное умножение/деление);

-

F, D — вычисления с плавающей точкой (F — float, D — double);

-

A — атомарные операции с памятью (общая память);

-

C — сжатые 16-битные инструкции (для устройств Интернета вещей (IoT));

-

E — встраиваемые системы (например, только 16 регистров, это нужно для маломощных процессоров, в том числе для IoT (Internet of Things)).

Если вам нужно будет работать с IoT-устройствами, то стоит использовать расширения C и E.

Применение RISC-V для Интернета вещей

Почему я так убежден, что RISC-V идеально подходит для Интернета вещей? Прежде всего все знают, как в IoT важны низкие цены. Здесь мы имеем дело с открытой архитектурой, за которую не нужно платить лицензию, как в случае, если вы, например, работаете с ARM. Далее, эта архитектура оптимизирована под низкое энергопотребление. В силу модульности вы берете на свой микропроцессор только то, что вам нужно, используйте расширения, которые нужны в вашем приложении, а всё остальное вы можете выкинуть.

Одно из агентств, занимающееся аналитикой компьютерной индустрии, дало оценку того, как будет развиваться RISC-V к 2025 году. Согласно прогнозам, доля RISC-V в IoT будет приближаться к 30%, в то время, как в других вещах, таких как индустриальные применения и автомобили, проникновение RISC-V будет гораздо меньшим. Таким образом, взлет RISC-V я ожидаю в области именно Интернета вещей.

Что очень важно: Интернет вещей страдает тем, что компьютерные хакеры чувствуют себя там, как дома. Это реально большая проблема. Большие компании не занимаются IoT, это удел маленьких компаний, там, где мало ресурсов и мало специалистов по компьютерной безопасности, в результате Интернет вещей — это охотничьи угодья для хакеров.

RISC-V с самого начала проектировался так, чтобы обеспечить необходимый уровень защиты. Здесь по умолчанию есть поддержка Trusted Execution Environment (TEE), позволяющей разделить доверенный код от недоверенного. Она лежит в основе обеспечения компьютерной безопасности на уровне железа.

С самого начала архитектура RISC-V поддерживает привилегированное исполнение расширений и защиту памяти. Это неотъемлемая часть архитектуры RISC-V и это будет на всех уровнях, начиная от крошечных одноядерных микропроцессоров для Интернета вещей, заканчивая мощными серверными микроконтроллерами. В качестве примера приведу Secure IoT stack от компании Hex-Five.

Начало работы с RISC-V

Если вы хотите изучить RISC-V, то на рынке существует масса отладочных плат, на которых вы можете начать разработку. У организации RISC-V International есть веб-страничка, на которых содержится список плат для разработчиков.

Кроме того, эта организация имеет программу Developer Boards по раздаче плат первопроходцам (early adopters) и образовательным учреждениям. Если вы подадите заявку в RISC-V International и убедите её в том, что занимаетесь интересными с точки зрения организации вещами, то производители этих плат могут вам дать их бесплатно.

В качестве примеров я приведу знакомые многим платы:

-

Sipeed Maixduino Kit для AI + IoT под RISC-V;

Если RISC-V вас заинтересовала, то следующий шаг – это самообразование. Я бы рекомендовал взять онлайн-курсы. Привожу здесь два таких курса:

-

«Введение в RISC-V» о международном сообществе RISC-V на платформе EdX (это небольшой курс, можно пройти за день-два);

-

RVfpga: Complete Courses in Computer Architecture & SoC Design от Imagination Technologies, чтобы поиграться с RISC-V, если у вас есть опыт работы с FPGA (ПЛИС, Программируемые логические интегральные схемы). Здесь вы можете воссоздать RISC-V на FPGA и писать для него программы на ассемблере.

Если вы хотите почитать книги, то рекомендую следующие:

-

Харрис Д.М., Харрис С.Л., “Цифровая схемотехника и архитектура компьютера: RISC-V” (классическая книга по логическому дизайну, последнее издание посвящено архитектуре RISC-V, на русском вышла в феврале 2022);

-

D. Patterson, J.L. Hennessy, ”Computer Organization and Design RISC-V Edition: The Hardware Software Interface” (от создателей архитектуры RISC-V, на русский язык пока не переведена);

-

D. Patterson, A. Waterman, “The RISC-V Reader: An Open Architecture Atlas”; (атлас, в деталях рассказывающий об устройстве архитектуры RISC-V, на русский язык пока не переведена).

Также мне нравится Telegram-канал, который ведёт преподаватель МИЭТ Михаил Попов, рассказывая о компьютерных архитектурах на примере RISC-V.

Спасибо за внимание!

Об авторе

Станислав Владимирович Полонский

Руководитель управления перспективных исследований и разработок Исследовательского центра Samsung в России

Канд. физ.-мат. наук

ссылка на оригинал статьи https://habr.com/ru/company/samsung/blog/668810/

Добавить комментарий