В данном мануале мы подробно рассмотрим настройку системы электрических ограничений (Constraint Editor System) в САПР Xpedition/PADS Professional, при работе с высокоскоростными интерфейсами на примере DDR памяти.

Будут разобраны следующие темы:

-

Обзор DDR

- Определения DDR и SDRAM

- Основные требования к проектам с использованием DDR

- Нюансы задания ограничений для схем с DDR

-

Определение импеданса

- Использование редактора стэкапа (Stackup Editor) в менеджере ограничений для вычисления ширины и контроля импеданса одиночного проводника на заданном слое

- Использование редактора стэкапа для расчета ширины и зазора между трассами для контроля импеданса в дифференциальной паре

- Использование редактора стэкапа для расчета ширины и зазора между трассами для контроля импеданса в дифференциальной паре

-

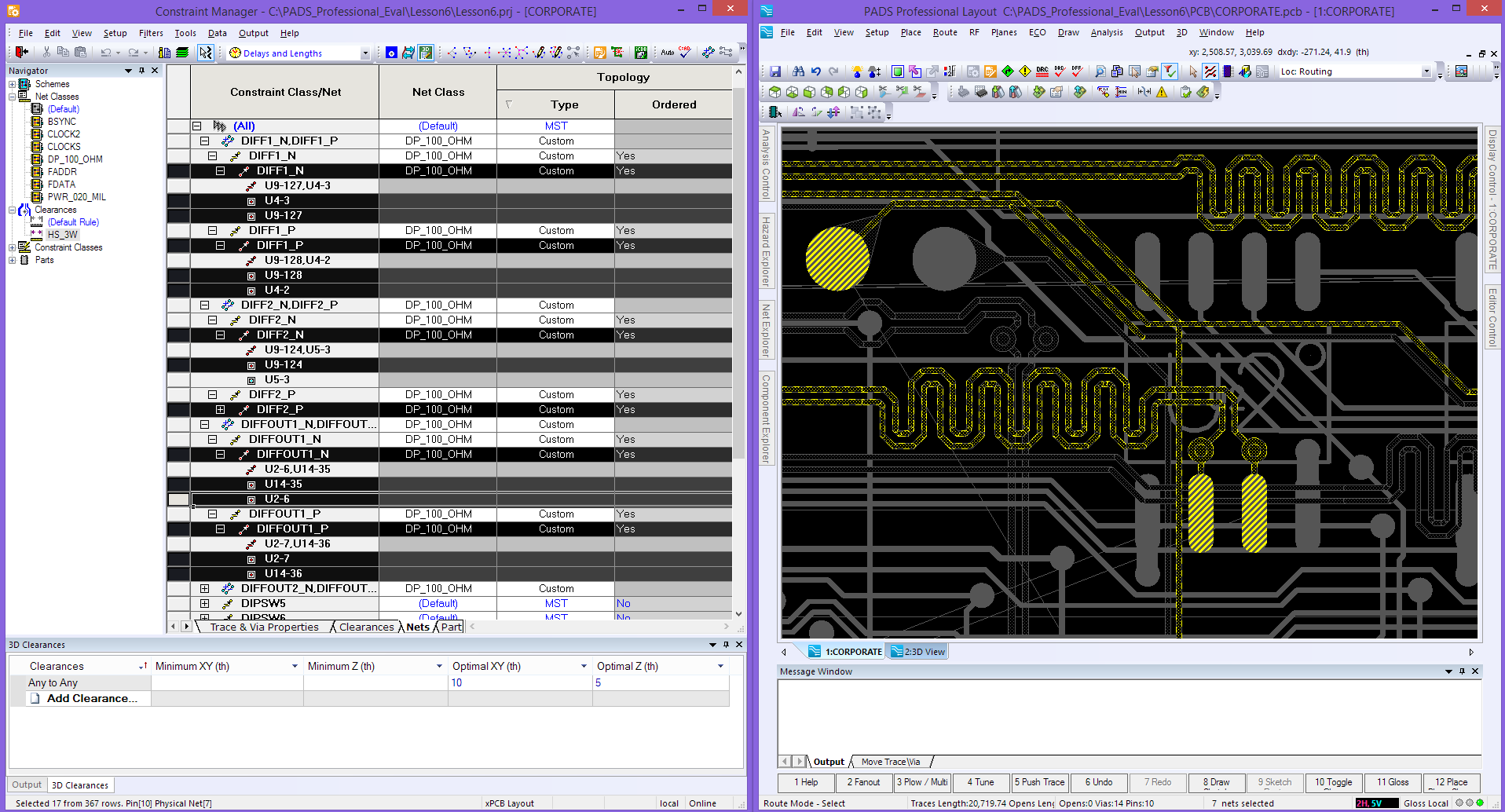

Выравнивание трасс по длине и времени распространения сигнала

- Различные методы для назначения ограничений по задержке

- Создание и использование пар контактов

- Использование констант и переменных

- Настройка минимальных и максимальных правил задержки

- Установка согласованных длин

- Работа с иерархией при настройке согласованной длины

- Знакомство с формулами задержки

- Настройка формул

- Использования констант и переменных в формулах

-

Типы и настройка кастомной топологии

- Назначение типов контактов (источник, нагрузка, терминатор)

- Изучение типов топологии

- Создание пользовательской топологии

- Создание пар контактов

-

Работа с дифференциальными сигналами

- Демонстрация влияния ввода ограничений при редактировании дифф. пар

- Расщепление дифф. пар

- Использования диалогового окна Diff Pair в Editor Control

-

Наводки и правила параллельности

- Обзор параллелизма и перекрестных помех

- Создание правил параллелизма

- Создание правил перекрестных помех

- Назначение правил для Nets/Classes

- Отображение ошибок правил параллельности

- Отображение ошибок правил перекрёстных помех

- Исправление ошибок параллельности

-

Шаблоны ограничений

- Создание шаблона ограничения

- Вкладка «шаблон ограничений»

- Назначение шаблона группе сигналов

- Экспорт шаблона в другую базу данных

- Шаблоны ограничений для трассировки DDR3

- Создание шаблона ограничений для трассировки DDR3

- Пример трассировки сегмента DDR3

- Изменение шаблона, для трассировки последующих сегментов

-

Инструмент Target Length и Manual Tuning

- Использование диалогового окна Target Lengths для выравнивания согласованных групп сигналов, используя метод “Tune this cluster using tuning rules in Editor Control” и «Easy Tune»

- Использование функции ручной настройки (manual tuning) для более точного выравнивания проводников

- Дополнительные разделы, связанные с определением общей длины проводников

Приятного просмотра

*Рассмотренные на данном вебинаре приемы и техники подходят как для PADS Professional, так и для Xpedition.

ссылка на оригинал статьи https://habr.com/company/nanosoft/blog/426879/

Добавить комментарий